Reduced instruction set computer facts for kids

A Reduced Instruction Set Computing (RISC, pronounced "risk") is a way to design a computer's main brain, called the CPU. Imagine a CPU as a chef. A RISC chef knows a few simple cooking steps really well. This means they can cook many dishes very quickly by doing lots of simple steps one after another.

RISC was created as a different way to build CPUs compared to older designs, which are now called CISC. While RISC and CISC are the main types, there are other ways to design CPUs too.

Contents

How RISC Processors Work

The main idea behind RISC processors is to keep their core design simple. This simplicity allows engineers to add more "workspaces" inside the CPU. These workspaces help the CPU do more tasks at the same time.

RISC CPUs use two main methods to work faster:

- Instruction level parallelism (ILP): This means the CPU can start working on a new instruction even before the previous one is fully finished. It's like a chef preparing ingredients for the next dish while the current one is still cooking.

- Thread level parallelism (TLP): This allows the CPU to handle many different tasks or "threads" at the same time. Imagine a chef cooking multiple dishes for different customers all at once.

Key Features of RISC

RISC processors have several features that help them be fast and efficient:

- Simple Instructions: All instructions look similar and are the same size. This makes it easier and faster for the CPU to understand what to do.

- Many Registers: CPUs use special storage spots called "registers" to hold data they are working on. RISC CPUs have many general-purpose registers, which makes it easier for computer programs to use them.

- Simple Ways to Find Data: RISC CPUs use easy methods to find data in the computer's memory. If a complex way is needed, the CPU breaks it down into several simple steps.

- Few Data Types: RISC CPUs handle only a few basic types of data directly. More complex data types are handled by combining these basic operations.

Famous RISC Processors

Many well-known computer chips use the RISC design. Some examples you might have heard of include:

- ARM: Found in almost all smartphones and tablets.

- MIPS: Used in many older game consoles and networking devices.

- Power Architecture: Used in some Apple computers and game consoles like the Xbox 360 and PlayStation 3.

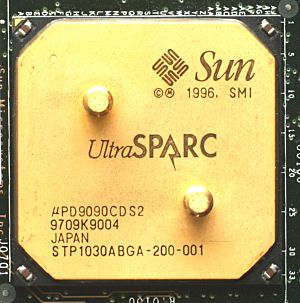

- SPARC: Used in powerful servers.

Other RISC processors include Alpha, ARC, AVR, PA-RISC, and PIC.

Images for kids

See also

In Spanish: Reduced instruction set computing para niños

In Spanish: Reduced instruction set computing para niños