Instruction pipelining facts for kids

Instruction pipelining is a clever trick used in modern computer processors. It helps them do more work faster. Think of it like an assembly line in a factory. Instead of building one car at a time from start to finish, many cars are being built at different stages all at once.

The main idea is to break down each computer instruction into several smaller, independent steps. Each step has its own storage area. This way, the computer's brain (the CPU) can handle instructions much faster. It works at the speed of the slowest step, but because many steps are happening at the same time, the overall speed goes up a lot.

The word "pipeline" comes from the idea that each step carries a small part of an instruction, like drops of water moving through pipes. Each step is connected to the next, just like water pipes.

Most modern CPUs work with a "clock." This clock sends out signals that tell the CPU when to do things. Inside the CPU are tiny electronic switches called flip-flops. When a clock signal arrives, these switches store new information. Then, the CPU's logic circuits take some time to figure out what to do with this new information. By breaking down the work into smaller pieces and putting these switches between them, the time needed for each piece of work is much shorter. This means the clock can tick faster, making the CPU work quicker.

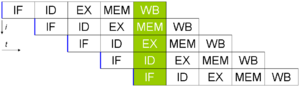

For example, a common type of computer, called a RISC machine, often breaks down instruction processing into five main stages:

- Instruction fetch: The CPU gets the next instruction from memory.

- Instruction decode and register fetch: The CPU figures out what the instruction means and gets any data it needs.

- Execute: The CPU performs the actual operation (like adding numbers).

- Memory access: If needed, the CPU reads or writes data to memory.

- Register write back: The CPU stores the result of the operation.

Processors that use pipelining have different sections (called stages) that can work on different parts of instructions at the same time. These stages are linked together, forming a chain. This setup greatly reduces the total time it takes to process many instructions.

Without pipelining, some parts of the CPU would be sitting idle while others are busy. Pipelining helps keep more parts of the CPU busy at the same time. This doesn't make a single instruction finish faster, but it makes the CPU complete many instructions much more quickly overall.

A pipeline is called fully pipelined if it can start a new instruction every time the clock ticks. If it can't, it has "wait cycles" that slow things down.

Contents

Why Pipelining is Great (and Not So Great)

Awesome Benefits of Pipelining

Pipelining makes processors much faster. It doesn't make one instruction finish quicker, but it lets the processor handle many instructions at the same time. This greatly increases the "throughput," which is how much work gets done per second.

- The more stages a pipeline has, the more instructions a processor can work on at once. This also reduces the delay between finishing one instruction and the next. Most modern computer brains use at least 2 stages, and some have 30 or 40!

- Pipelining allows the CPU's Arithmetic logic unit (the part that does math) to be designed for speed, even if it becomes more complex.

- In theory, pipelining can make a processor work as many times faster as it has stages. This is true if the code being run is perfect for pipelining.

- Pipelined CPUs often run at much higher speeds than the computer's main memory (RAM). This helps make the whole computer faster.

Challenges of Pipelining

Even though pipelining is great, it has some challenges. However, computer designers and programmers have found many ways to solve most of these problems. Here are some common drawbacks:

- A processor without pipelining is simpler and cheaper to build. It only does one instruction at a time, which avoids certain delays that pipelining can cause.

- Adding the electronic switches between pipeline stages can slightly increase the time it takes for a single instruction to complete, compared to a non-pipelined processor.

- It's harder to guess how fast a pipelined processor will be. Its performance can change a lot depending on the program it's running.

- Long pipelines (with many stages) have a big disadvantage when a program "branches." A branch is like a fork in the road for the program. The processor doesn't know which path to take next until the branch instruction is finished. When this happens, the entire pipeline might need to be "flushed" (cleared out), which means all the instructions that were in progress get thrown away. This can make the processor slow down a lot, sometimes even slower than a non-pipelined one. Designers try to predict which way the branch will go to avoid this.

- Not all instructions are independent. Sometimes, one instruction needs the result of a previous instruction before it can start. If the previous instruction is still in the pipeline, the current instruction has to wait. This causes a "stall" or a wasted clock cycle. Luckily, techniques like "forwarding" can help reduce these waits.

- Programs that change their own instructions while running (called self-modifying programs) might not work correctly on pipelined systems. This is because the instructions might already be loaded into a waiting area, so the changes won't affect them right away.

- Hazards: When a programmer writes code, they usually assume that each instruction finishes before the next one starts. Pipelining breaks this assumption because multiple instructions are running at once. If this causes a program to act unexpectedly, it's called a hazard. There are different ways to fix or work around these hazards, like pausing the pipeline or sending results directly to where they're needed.

Examples of Pipelining

A Simple Pipeline Example

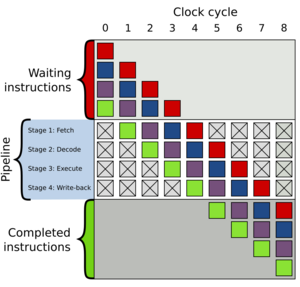

Imagine a simple pipeline with four stages:

- Fetch: Get the instruction.

- Decode: Understand the instruction.

- Execute: Do the instruction's task.

- Write-back: Save the result.

Let's see how four different instructions (green, purple, blue, red) would go through this pipeline:

| Time | What's Happening |

|---|---|

| 0 | Four instructions are waiting to be processed. |

| 1 | The green instruction is fetched from memory. |

| 2 | The green instruction is decoded. The purple instruction is fetched. |

| 3 | The green instruction is executed. The purple instruction is decoded. The blue instruction is fetched. |

| 4 | The green instruction's results are saved. The purple instruction is executed. The blue instruction is decoded. The red instruction is fetched. |

| 5 | The green instruction is finished. The purple instruction's results are saved. The blue instruction is executed. The red instruction is decoded. |

| 6 | The purple instruction is finished. The blue instruction's results are saved. The red instruction is executed. |

| 7 | The blue instruction is finished. The red instruction's results are saved. |

| 8 | The red instruction is finished. |

| 9 | All instructions are done! |

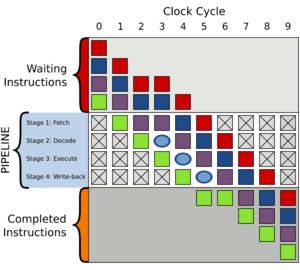

Pipeline Bubble

Sometimes, something might cause a delay in the pipeline. This creates a "bubble," which means nothing useful happens in that stage for a clock cycle. For example, if the purple instruction is delayed, the decoding stage might be empty for a moment. Everything behind the purple instruction also gets delayed, but instructions ahead of it continue as normal.

In our example above, if a bubble happens, it might take 8 clock ticks instead of 7 to finish all instructions. A bubble is like a pause or a "no operation" step in the pipeline.

Example 1: Adding Numbers

Let's say a computer needs to add two numbers, A and B, and put the answer in C. The instruction might look like `ADD A, B, C`. A pipelined processor would break this down into smaller steps, like:

LOAD A, R1 (Get number A and put it in a temporary spot R1) LOAD B, R2 (Get number B and put it in a temporary spot R2) ADD R1, R2, R3 (Add R1 and R2, put the answer in R3) STORE R3, C (Save the answer from R3 into memory location C) LOAD next instruction (Get the next instruction ready)

Here, 'R1', 'R2', and 'R3' are special temporary storage areas inside the CPU called registers.

In this example, the pipeline has three stages: load, execute, and store. On a non-pipelined processor, only one stage would work at a time. But with pipelining, all stages can be busy at once, working on different instructions. So, while one instruction is being executed, another is being decoded, and a third is being fetched.

Example 2: A 3-Stage Pipeline

Let's look at another example with a theoretical 3-stage pipeline:

| Stage | What it Does |

|---|---|

| Load | Reads an instruction from memory |

| Execute | Performs the instruction's task |

| Store | Saves the result in memory or registers |

And here's a simple list of instructions:

LOAD #40, A ; put the number 40 into location A

MOVE A, B ; copy what's in A into location B

ADD #20, B ; add 20 to what's in B

STORE B, 0x300 ; save what's in B into memory spot 0x300Here's how it would run:

| Load | Execute | Store |

|---|---|---|

| LOAD |

The `LOAD` instruction is fetched from memory.

| Load | Execute | Store |

|---|---|---|

| MOVE | LOAD |

The `LOAD` instruction is now executing (putting 40 into A), while the `MOVE` instruction is being fetched.

| Load | Execute | Store |

|---|---|---|

| ADD | MOVE | LOAD |

The `LOAD` instruction is now in the "Store" stage, saving the number 40 into register A. At the same time, the `MOVE` instruction is executing. Since `MOVE` needs the value from A, it has to wait for the `LOAD` instruction to finish its "Store" stage.

| Load | Execute | Store |

|---|---|---|

| STORE | ADD | MOVE |

The `STORE` instruction is being loaded. The `ADD` instruction is calculating. The `MOVE` instruction is finishing up.

Sometimes, an instruction needs the result of a previous one, like our `MOVE` example. If instructions are run out of their original order because of pipelining, and they need to use the same memory spot, it can lead to the "hazards" we talked about earlier.

Related pages

- Pipeline (computing)

- Parallel computing

- Instruction-level parallelism

See also

In Spanish: Segmentación de instrucciones para niños

In Spanish: Segmentación de instrucciones para niños