Superscalar processor facts for kids

A superscalar processor is a special kind of CPU (the "brain" of a computer). It can do many things at once, which is called instruction-level parallelism. Unlike a regular processor (called a scalar processor) that does one task at a time, a superscalar processor can handle several tasks at the same time. It sends these tasks to different parts of the processor called execution units.

This makes the computer much faster because it can finish more tasks in the same amount of time. These execution units are like different tools inside one big workshop (the CPU). They aren't separate mini-CPUs.

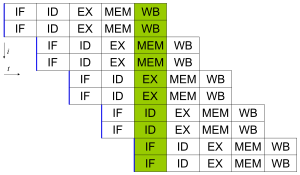

Superscalar processors often use a technique called pipelining. Pipelining is like an assembly line where different parts of a task are done at the same time. Superscalar processing is different because it uses many tools (execution units) to do many tasks at once.

Superscalar CPUs have some key features:

- They take instructions from a normal, step-by-step list.

- The CPU checks on its own if tasks depend on each other.

- They can finish more than one instruction in each clock cycle.

Contents

History of Superscalar Processors

The idea of superscalar processors started a long time ago. The Seymour Cray's CDC 6600 computer from 1964 is often seen as the first design like this. The IBM System/360 Model 91 from 1967 was another early example.

The first single-chip superscalar microprocessors for everyday use came out in the late 1980s. These included the Motorola MC88100 (1988) and the Intel i960CA (1989). RISC (Reduced Instruction Set Computer) microprocessors were the first to use this technology. This is because RISC designs were simpler, leaving more space for extra execution units.

Today, almost all general-purpose CPUs made since about 1998 are superscalar. This means the computer you use probably has a superscalar processor inside! Only very small or low-power devices might not use them.

The P5 Pentium was the first superscalar processor for x86 computers. Later designs, like the P6 Pentium Pro, became even better. They could break down complex instructions into smaller steps called micro-ops. This helped them do even more tasks at the same time.

Scalar vs. Superscalar Processors

The simplest processors are called scalar processors. A scalar processor usually handles one or two pieces of data at a time for each instruction. Think of it like doing one math problem at a time.

A superscalar processor is different. It still works on one piece of data per instruction, but it has many execution units. This means it can work on many different instructions at the same time. It's like having many people solving different math problems all at once.

The main goal of a superscalar CPU is to keep all its execution units busy. Early superscalar CPUs might have had two ALUs (for basic math) and one FPU (for more complex math). Newer designs, like the PowerPC 970, have many more. They can have four ALUs, two FPUs, and two SIMD units (for handling lots of data at once).

If the processor can't keep all these units busy, it won't be much faster than a simpler, cheaper design. A superscalar processor can usually complete more than one instruction in each machine cycle.

How Superscalar Processors Work

In a superscalar CPU, a special part called the dispatcher reads instructions from the computer's memory. It then figures out which instructions can be run at the same time. After that, it sends each instruction to one of the many execution units inside the CPU.

So, you can imagine a superscalar processor as having many parallel "pipelines." Each pipeline works on instructions at the same time, all from the same list of tasks.

Limits of Superscalar Design

Even though superscalar processors are fast, there are limits to how much faster they can get. These limits come from three main areas:

- How many tasks can truly be done at the same time.

- How complex it is to check for task dependencies.

- How the processor handles "branch" instructions (like "if-then" statements).

Some computer programs have tasks that don't depend on each other. For example, if you have two math problems like "a = b + c" and "d = e + f", they can be solved at the same time. But if one task needs the result of another, like "a = b + c" and then "b = e + f", they might not be able to run in parallel.

The CPU must always check if tasks depend on each other. If it doesn't, it could get the wrong answer. This checking takes time and makes the processor more complex. Even with super-fast technology, there's a limit to how many instructions can be sent out at once.

Also, if a program has many tasks that depend on each other, the processor can't speed up as much. This is because it has to wait for one task to finish before starting the next.

Other Ways to Make Processors Faster

Because of these limits, scientists and engineers look for other ways to make computers faster. Some of these ideas include:

- Very long instruction word (VLIW): Here, the computer program itself tells the processor which tasks can run at the same time. This takes the burden off the hardware.

- Simultaneous multithreading (SMT): This allows a superscalar processor to work on tasks from different programs at the same time. It helps use all the processor's resources better.

- Multi-core computing: This is when a single processor chip has several complete CPUs (called "cores") inside it. Each core can work on its own set of tasks.

Superscalar processors are different from multi-core processors. A superscalar processor has many small execution units inside one CPU. A multi-core processor has several full CPUs (cores) working together.

These different techniques can often be combined. For example, a multi-core CPU can have each core be an independent processor that is also superscalar. Some processors even have special parts for handling vector tasks, which are good for things like graphics.

See also

In Spanish: Superescalar para niños

In Spanish: Superescalar para niños

- Eager execution

- Hyper-threading

- Simultaneous multithreading

- Out-of-order execution

- Speculative execution