Superscalar facts for kids

A superscalar CPU is a special kind of computer processor that can do more than one thing at the same time. Think of it like a chef who can chop vegetables and stir a pot at the same time, instead of doing one task after the other. This helps the computer work faster without needing a higher clock rate (which is how many operations a CPU can do per second).

A superscalar CPU works by having several "worker units" inside it. These units are like different tools a chef might have, such as a special unit for adding numbers (an ALU) or one for complex math (a FPU). When the CPU gets instructions, it figures out which ones can be done at the same time and sends them to these different worker units. This is called instruction dispatching.

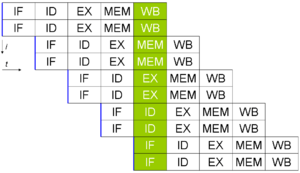

Most superscalar CPUs also use a method called pipelining. This is like an assembly line where different parts of an instruction are worked on at the same time, but in different stages.

Here are some key things about how superscalar CPUs work:

- They get instructions from a list, one after another.

- The CPU can figure out if one instruction needs to wait for another to finish (this is called a data dependency).

- They can read many instructions at once during each clock cycle.

Imagine a regular CPU (a scalar processor) as someone doing one task at a time. A vector processor can handle many pieces of data with one instruction, like a machine that chops many vegetables at once. A superscalar processor is a mix:

- Each instruction still works on one piece of data.

- But, the CPU has many duplicate worker units. This means it can handle many independent instructions at the same time.

Inside a superscalar CPU, there's a special part called an instruction dispatcher. This dispatcher reads instructions and decides which ones can run at the same time. It then sends them to the available worker units. The goal of designing a superscalar CPU is to make this dispatcher very smart so it can keep all the worker units busy as much as possible.

Today, almost all general-purpose CPUs are superscalar. A typical superscalar CPU might have several ALUs, FPUs, and other units. If the dispatcher can't keep these units busy, the CPU won't perform as well as it could.

Contents

Why Superscalar CPUs Have Limits

Even though superscalar CPUs are fast, there are limits to how much faster they can get:

- Not all instructions can run at the same time: Some instructions depend on the results of others. If there are too many of these "dependencies" in the instruction list, the CPU has to wait, which slows things down.

- The dispatcher can get complicated: The part of the CPU that figures out which instructions can run in parallel (the dispatcher) can become very complex and take time to do its job.

Even if the dispatcher could check dependencies super fast, the number of instructions that can run at the same time is still limited by how much "parallelism" is built into the computer code itself. There's a practical limit to how many instructions can be sent out at once, usually around five or six.

Other Ways to Make CPUs Faster

Superscalar design is just one way to make CPUs faster. Here are some others:

Simultaneous Multithreading (SMT)

This technique helps superscalar CPUs use their resources even better. SMT allows a single CPU core to run multiple independent sets of instructions (called threads) at the same time. This means if one thread is waiting for something, another thread can use the CPU's worker units, keeping them busy.

Multi-core Processors

Superscalar CPUs are different from multi-core processors. A superscalar CPU has multiple worker units inside *one* processor core. A multi-core processor, on the other hand, has several complete processor cores on a single chip. Each core can run its own set of instructions. So, a multi-core processor is like having several separate chefs, while a superscalar processor is like having one very efficient chef with many tools and hands.

Pipelined Processors

Superscalar processors are also different from simply pipelined CPUs. In a pipelined CPU, different parts of one instruction are worked on at the same time in different stages, like an assembly line. Superscalar CPUs take this a step further by running multiple *different* instructions at the same time, each potentially going through its own pipeline.

It's important to know that these different techniques are not exclusive. They can often be combined in one processor! For example, a modern computer might have a multi-core CPU where each core is a superscalar processor that also uses pipelining and SMT. Some even include vector capabilities for even faster processing of large amounts of data.

Related pages

- Parallel computing

- Instruction level parallelism

- Simultaneous multithreading (SMT)

- Multi-core processor

See also

In Spanish: Superescalar para niños

In Spanish: Superescalar para niños