ARM architecture family facts for kids

|

|

| Designer |

|

|---|---|

| Bits | 32-bit, 64-bit |

| Introduced | 1985 |

| Design | RISC |

| Type | Register-Register |

| Branching | Condition code, compare and branch |

| Open | Proprietary |

| Introduced | 2011 |

|---|---|

| Version | ARMv8-R, ARMv8-A, ARMv8.1-A, ARMv8.2-A, ARMv8.3-A, ARMv8.4-A, ARMv8.5-A, ARMv8.6-A, ARMv8.7-A, ARMv8.8-A, ARMv8.9-A, ARMv9.0-A, ARMv9.1-A, ARMv9.2-A, ARMv9.3-A, ARMv9.4-A |

| Encoding | AArch64/A64 and AArch32/A32 use 32-bit instructions, T32 (Thumb-2) uses mixed 16- and 32-bit instructions |

| Endianness | Bi (little as default) |

| Extensions | SVE, SVE2, SME, AES, SHA, TME; All mandatory: Thumb-2, Neon, VFPv4-D16, VFPv4; obsolete: Jazelle |

| Registers | |

| General purpose | 31 × 64-bit integer registers |

| Floating point | 32 × 128-bit registers for scalar 32- and 64-bit FP or SIMD FP or integer; or cryptography |

| Version | ARMv9-R, ARMv9-M, ARMv8-R, ARMv8-M, ARMv7-A, ARMv7-R, ARMv7E-M, ARMv7-M, ARMv6-M |

|---|---|

| Encoding | 32-bit, except Thumb-2 extensions use mixed 16- and 32-bit instructions. |

| Endianness | Bi (little as default) |

| Extensions | Thumb-2, Neon, Jazelle, AES, SHA, DSP, Saturated, FPv4-SP, FPv5, Helium |

| Registers | |

| General purpose | 15 × 32-bit integer registers, including R14 (link register), but not R15 (PC) |

| Floating point | Up to 32 × 64-bit registers, SIMD/floating-point (optional) |

| Version | ARMv6, ARMv5, ARMv4T, ARMv3, ARMv2 |

|---|---|

| Encoding | 32-bit, except Thumb extension uses mixed 16- and 32-bit instructions. |

| Endianness | Bi (little as default) in ARMv3 and above |

| Extensions | Thumb, Jazelle |

| Registers | |

| General purpose | 15 × 32-bit integer registers, including R14 (link register), but not R15 (PC, 26-bit addressing in older) |

| Floating point | None |

ARM (which used to stand for Advanced RISC Machines) is a special type of computer processor design. Think of it as a blueprint for how a computer's "brain" works. These designs are used in many different electronic devices. Arm Ltd. creates these blueprints and lets other companies use them to build their own products. These products include smartphones, laptops, and even supercomputers!

ARM processors are popular because they don't cost much, use very little power, and don't get too hot. This makes them perfect for devices that run on batteries, like your phone or tablet. But ARM processors are also powerful enough for desktops and servers. For example, the world's fastest supercomputer, Fugaku, used ARM chips from 2020 to 2022. By 2022, over 230 billion ARM chips had been made, making ARM the most common type of processor design in the world!

Over the years, ARM designs have changed and improved. The first ARM chip, ARM1, could handle 32-bit information but only had a 26-bit address space. This limited it to 64 megabytes of main memory. Later versions, like ARMv3, could use a full 32-bit address space. In 2011, the ARMv8-A design added support for 64-bit information, making processors even more powerful. ARM has also added special features like "Thumb" instructions, which make code smaller, and "Jazelle," which helped with Java programs.

Contents

- The Story of ARM: How It Started

- How ARM Licenses Its Designs

- ARM Processor Designs (Cores)

- Understanding ARM's 32-bit Architecture

- Security Features

- 64/32-bit Architecture

- Operating System Support

- Images for kids

- See also

The Story of ARM: How It Started

The BBC Micro Computer

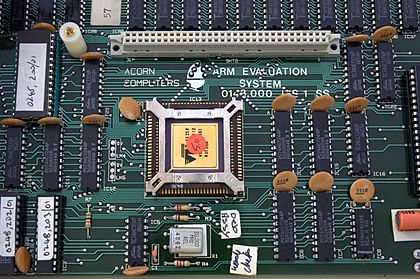

The story of ARM began with a company called Acorn Computers. In 1981, they released a very popular computer called the BBC Micro. This computer was special because it ran faster than other computers at the time, like the Apple II. It used a special trick with its memory to achieve this speed.

Designing a New Computer

In 1981, the IBM Personal Computer came out. It used a newer, more powerful 16-bit processor. Acorn wanted to create a new computer that was ten times faster than the BBC Micro but cost the same. They also saw new computers like the Apple Lisa that had a graphical user interface (GUI), which meant you could click on icons instead of typing commands. This seemed like the future!

Acorn's engineers looked at all the available processors. They found that most 16-bit and 32-bit processors were expensive and needed many extra chips to work. This would make their new computer too costly. Two important things happened next that changed everything for Acorn:

- Reports from the University of California, Berkeley suggested that even a simple chip design could be very powerful.

- Acorn engineers Steve Furber and Sophie Wilson visited another company and saw how easy it was to design chips. This made them decide to design their own processor.

In late 1983, they started the "Acorn RISC Machine" project.

Smart Design Choices

The ARM design was inspired by the simple, yet powerful, MOS Technology 6502 processor used in the BBC Micro. One clever idea was to make it easy for the processor to handle interrupts (signals that tell the computer to stop what it's doing and do something else). To do this quickly, the ARM design limited the memory it could directly access to 64 megabytes. This allowed the computer to save its current work very fast when an interrupt happened.

Another smart idea was to make the processor work well with a new type of memory called "page mode DRAM." This memory could work twice as fast if the data was in the same "page." ARM added special instructions to take advantage of this, which was very important for graphics.

Sophie Wilson created a computer program that simulated how the new processor would work. This showed the Acorn team they were on the right track. In October 1983, the official ARM project began.

The First ARM Chips

Acorn worked with a company called VLSI Technology to make the actual chips. The very first ARM chip, called ARM1, worked perfectly when it was first tested on April 26, 1985. It ran at 6 MHz.

The ARM1 was first used as a second processor for the BBC Micro. This helped the team develop more software and design the next version. Sophie Wilson even rewrote the BBC BASIC programming language using ARM's own language, which helped test the new chip.

ARM2: Faster and Smarter

The ARM2 chip came out in late 1986, running at 8 MHz, and later at 10 to 12 MHz. A big improvement was adding a "Booth multiplier," which made multiplication much faster. It also had a new "Fast Interrupt reQuest" (FIQ) mode that made handling urgent tasks even quicker.

The ARM2 was very powerful for its time. It was about seven times faster than a typical 68000-based computer like the Amiga. It was also twice as fast as an Intel 80386 chip. What made it special was its simplicity. It had only 30,000 transistors, compared to the 68,000 in Motorola's 68000 chip. This made it use less power and generate less heat.

A later version, ARM3, added a small memory called a "cache" to make it even faster. The ARM6 extended the memory addressing to 32 bits, allowing access to more memory.

Advanced RISC Machines Ltd. – ARM6

In the late 1980s, Apple Computer and VLSI Technology joined Acorn to work on new ARM designs. In 1990, the ARM design team became its own company, called Advanced RISC Machines Ltd. (which later became ARM Ltd.). Their work led to the ARM6 chip, released in 1992. Apple used the ARM6-based ARM610 in their Apple Newton PDA (a type of early tablet).

Who Uses ARM Chips?

In 1994, Acorn used the ARM610 in their RiscPC computers. Other companies also started using ARM designs. DEC created a powerful ARM chip called StrongARM. This chip used very little power. Later, Intel took over StrongARM and developed its own version called XScale. Even with all these changes, the number of transistors in the ARM core stayed small, making it very efficient.

By 2005, about 98% of all mobile phones used at least one ARM processor. By 2010, companies had shipped 6.1 billion ARM-based processors. This included 95% of smartphones and 35% of digital televisions. ARM is truly everywhere!

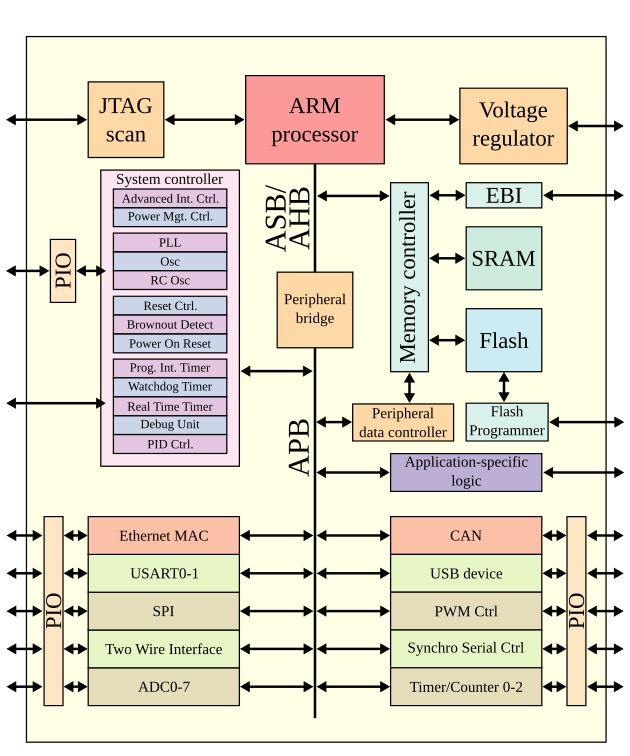

How ARM Licenses Its Designs

Arm Ltd. makes money by selling licenses for its processor designs, called "IP cores." Other companies then use these designs to create their own chips, like microcontrollers (MCUs) or systems-on-chips (SoCs). An SoC combines many parts, like the processor, memory, and other features, onto a single chip. This makes devices smaller and cheaper to build.

The ARM designs used in smartphones and tablets usually range from ARMv5 to ARMv8-A. Many companies, like Nvidia, Samsung, Apple, and Texas Instruments, use ARM's core designs in their products.

Arm Ltd. offers different types of licenses. Some companies get a ready-to-use design. Others, who want more control, get the design in a format that allows them to make changes and improvements. This lets them create chips that are super fast or use very little power. While companies can't resell the ARM design itself, they can freely sell the chips and products they make using ARM's designs.

Some companies, like Qualcomm, can even get a "Built on ARM Cortex Technology" license. This allows them to make their own changes to ARM Cortex designs, and these changes are kept secret from other companies.

There's also an "Architectural license." This lets companies design their own CPU cores from scratch, as long as they follow the ARM instruction sets (the rules for how the processor understands commands). Companies like Apple, Intel, and Samsung have designed their own cores using an ARM architectural license.

In 2019, ARM introduced "ARM Flexible Access." This program gives companies access to many ARM designs for development. They only pay a license fee when they are ready to produce their chip.

ARM Processor Designs (Cores)

ARM offers many different processor designs, called "cores." These cores are grouped by their "architecture" (like ARMv7 or ARMv8) and what they are designed for (like "Application" for phones, "Real-time" for quick tasks, or "Microcontroller" for small devices).

| Architecture | Core bit-width |

Cores | Profile | Refe- rences |

|

|---|---|---|---|---|---|

| Arm Ltd. | Third-party | ||||

|

|

|

ARM1 |

|

||

|

|

|

ARM2, ARM250, ARM3 | Amber, STORM Open Soft Core |

|

|

|

|

|

ARM6, ARM7 |

|

||

|

|

|

ARM8 | StrongARM, FA526, ZAP Open Source Processor Core |

|

|

|

|

|

ARM7TDMI, ARM9TDMI, SecurCore SC100 |

|

||

|

|

|

ARM7EJ, ARM9E, ARM10E | XScale, FA626TE, Feroceon, PJ1/Mohawk |

|

|

|

|

|

ARM11 |

|

||

|

|

|

ARM Cortex-M0, ARM Cortex-M0+, ARM Cortex-M1, SecurCore SC000 |

|

||

|

|

|

ARM Cortex-M3, SecurCore SC300 | Apple M7 motion coprocessor |

|

|

|

|

|

ARM Cortex-M4, ARM Cortex-M7 |

|

||

|

|

|

ARM Cortex-M23, ARM Cortex-M33 |

|

||

|

|

|

ARM Cortex-R4, ARM Cortex-R5, ARM Cortex-R7, ARM Cortex-R8 |

|

||

|

|

|

ARM Cortex-R52 |

|

||

|

|

ARM Cortex-R82 |

|

|||

|

|

|

ARM Cortex-A5, ARM Cortex-A7, ARM Cortex-A8, ARM Cortex-A9, ARM Cortex-A12, ARM Cortex-A15, ARM Cortex-A17 | Qualcomm Scorpion/Krait, PJ4/Sheeva, Apple Swift (A6, A6X) |

|

|

|

|

|

ARM Cortex-A32 |

|

||

|

|

ARM Cortex-A35, ARM Cortex-A53, ARM Cortex-A57, ARM Cortex-A72, ARM Cortex-A73 | X-Gene, Nvidia Denver 1/2, Cavium ThunderX, AMD K12, Apple Cyclone (A7)/Typhoon (A8, A8X)/Twister (A9, A9X)/Hurricane+Zephyr (A10, A10X), Qualcomm Kryo, Samsung M1/M2 ("Mongoose") /M3 ("Meerkat") |

|

||

|

|

ARM Cortex-A34 |

|

|||

|

|

|

TBA | Cavium ThunderX2 |

|

|

|

|

|

ARM Cortex-A55, ARM Cortex-A75, ARM Cortex-A76, ARM Cortex-A77, ARM Cortex-A78, ARM Cortex-X1, ARM Neoverse N1 | Nvidia Carmel, Samsung M4 ("Cheetah"), Fujitsu A64FX (ARMv8 SVE 512-bit) |

|

|

|

|

ARM Cortex-A65, ARM Neoverse E1 with simultaneous multithreading (SMT), ARM Cortex-A65AE (also having e.g. ARMv8.4 Dot Product; made for safety critical tasks such as advanced driver-assistance systems (ADAS)) | Apple Monsoon+Mistral (A11) (September 2017) |

|

||

|

|

|

TBA |

|

||

|

|

TBA | Apple Vortex+Tempest (A12, A12X, A12Z), Marvell ThunderX3 (v8.3+) |

|

||

|

|

|

TBA |

|

||

|

|

ARM Neoverse V1 | Apple Lightning+Thunder (A13), Apple Firestorm+Icestorm (A14, M1) |

|

||

|

|

|

TBA |

|

||

|

|

TBA |

|

|||

|

|

|

TBA | Apple Avalanche+Blizzard (A15, M2), Apple Everest+Sawtooth (A16) |

|

|

|

|

|

TBA |

|

||

|

|

|

TBA |

|

||

|

|

|

TBA |

|

||

|

|

|

ARM Cortex-A510, ARM Cortex-A710, ARM Cortex-A715, ARM Cortex-X2, ARM Cortex-X3, ARM Neoverse E2, ARM Neoverse N2, ARM Neoverse V2 |

|

||

|

|

|

TBA |

|

||

|

|

|

ARM Cortex-A520, ARM Cortex-A720, ARM Cortex-X4 | Qualcomm Snapdragon 8 Gen 3, Mediatek Dimensity 9300 |

|

|

|

|

|

TBA |

|

||

|

|

|

TBA |

|

||

Where Are ARM Cores Used?

ARM cores are found in many devices you use every day.

- They power PDAs (old handheld devices) and smartphones.

- They are in Microsoft's Surface tablets and Apple's iPads.

- You can find them in Chromebook laptops.

- Your iPhone and iPod use ARM chips.

- Even Canon PowerShot digital cameras, the Nintendo Switch, and 3DS game consoles use ARM.

- TomTom GPS devices also rely on ARM.

In 2005, ARM helped develop the Manchester University's computer SpiNNaker. This computer used ARM cores to try and act like the human brain. ARM chips are also used in small, affordable computers like Raspberry Pi and BeagleBoard. These are popular for learning to code and building electronics projects because they are tiny, cheap, and use very little power.

Understanding ARM's 32-bit Architecture

The 32-bit ARM architecture, like the Armv7-A, was the most common type of processor in mobile devices around 2011. This architecture has different "profiles" for different uses:

- A-profile: For "Application" devices like smartphones.

- R-profile: For "Real-time" systems that need to respond very quickly.

- M-profile: For "Microcontroller" devices, which are small, simple computers.

How ARM Processors Work: CPU Modes

The 32-bit ARM architecture has several "CPU modes." Think of these as different ways the processor can operate. At any time, the CPU is in one mode, but it can switch modes if something important happens, like an interrupt (a signal asking for attention).

- User mode: This is the normal mode for running apps. It has limited access.

- Privileged modes: These modes have special access to the system. They are used for handling interrupts or when the system starts up.

ARM's Instruction Set

ARM processors use a special set of commands called an "instruction set." These commands tell the processor what to do.

- Load-store architecture: This means the processor loads data from memory into its internal storage (registers) to work on it, and then stores it back to memory.

- Registers: ARM has 16 special storage areas called "registers" that hold 32-bit information. These include the program counter (PC), which keeps track of where the program is.

- Fixed instruction width: Most ARM commands are 32 bits long. This makes it easier for the processor to understand and process them quickly.

To make up for its simple design, ARM uses some clever tricks:

- Conditional execution: Many ARM commands can be told to run only if a certain condition is true. This helps the processor avoid wasting time by skipping unnecessary steps.

- Barrel shifter: This allows the processor to quickly move or shift bits within a number, which is useful for calculations.

Math Instructions

ARM can do basic math like adding, subtracting, and multiplying. Some versions can also divide. ARM can multiply 32-bit numbers to get either a 32-bit or 64-bit result.

Registers Explained

Think of registers as small, super-fast scratchpads inside the CPU.

- Registers R0 through R7 are always available in all CPU modes.

- Registers R8 through R12 are mostly the same, except in a special "FIQ mode" for very fast interrupts.

- Registers R13 and R14 change depending on the privileged CPU mode. R13 is often used as the stack pointer (SP), which helps manage data for functions. R14 is the link register (LR), which stores the return address for function calls.

- R15 is the program counter (PC), which points to the next instruction to be run.

The Current Program Status Register (CPSR) holds important information about the processor's state, like the current mode and various flags (like whether a calculation resulted in zero or a negative number).

Conditional Commands

Almost every ARM command can be set to run only if a certain condition is met. This is like saying, "Only do this if X is true." This helps the processor run code more efficiently, especially for "if-then" statements in programming.

For example, if you want to find the greatest common divisor (GCD) of two numbers, you might write code like this:

; put 'a' in register r0, 'b' in r1

loop: CMP r0, r1 ; Compare r0 and r1. This sets flags like "equal," "greater than," or "less than."

SUBGT r0, r0, r1 ; If r0 was Greater Than r1, then r0 = r0 - r1.

SUBLT r1, r1, r0 ; If r0 was Less Than r1, then r1 = r1 - r0.

BNE loop ; If r0 and r1 were Not Equal, go back to 'loop'.

B lr ; Return from the function.Notice how `SUBGT` (subtract if greater than) and `SUBLT` (subtract if less than) only run when their conditions are true. This avoids needing extra "jump" commands, making the code faster.

Other Cool Features

ARM also lets you combine operations. For example, you can shift a number and then add it in one single command. This makes ARM programs very compact and efficient. ARM also has features like "PC-relative addressing," which means it can find data based on its current position in the program.

Pipelines and Performance

Modern ARM processors use "pipelines" to work faster. Imagine an assembly line:

- Stage 1: Fetch the instruction.

- Stage 2: Decode the instruction.

- Stage 3: Execute the instruction.

Older ARM chips had three stages, but newer ones like the Cortex-A8 have thirteen stages, allowing them to process many instructions at once.

Coprocessors

ARM allows adding "coprocessors," which are like specialized helper chips. These coprocessors can handle specific tasks, like image processing, very quickly.

Debugging ARM Chips

All modern ARM processors have special features for "debugging." Debugging means finding and fixing errors in computer programs. These features allow programmers to pause the code, step through it line by line, and set "breakpoints" to stop at specific points. This helps them understand what the program is doing and where it might be going wrong.

DSP and Multimedia Instructions

To make ARM better for things like sound and video, special "DSP" (Digital Signal Processing) instructions were added. These help with tasks like compressing audio or processing images.

Jazelle

Jazelle was a feature that allowed ARM processors to directly run Java bytecode, which is the code used by Java programs. This made Java programs run faster on ARM devices. However, this feature is no longer supported in newer ARM versions.

Thumb Instruction Set

To make programs smaller and use less memory, ARM introduced the Thumb instruction set in 1994. When in "Thumb state," the processor uses shorter, 16-bit commands. These commands do similar things to the regular 32-bit ARM commands but take up less space. This is very useful for devices with limited memory.

For example, on devices like the Game Boy Advance, some memory is fast and 32-bit, while most is slower and 16-bit. Using Thumb code for most of the program helps it run faster because less code needs to be loaded from the slower memory.

Thumb-2: The Next Step

Thumb-2 was introduced in 2003. It improved on Thumb by adding more 32-bit commands to the 16-bit set. This created a "variable-length" instruction set, meaning commands could be 16 or 32 bits long. The goal was to get the small code size of Thumb with the high performance of the full ARM instruction set.

All ARMv7 chips support Thumb-2. Processors in the Cortex-A and Cortex-R series can switch between ARM and Thumb-2 modes. However, chips in the Cortex-M series (for microcontrollers) only use the Thumb instruction set.

Floating-Point (VFP)

VFP (Vector Floating Point) is a special part of the ARM architecture that helps with "floating-point" math. This type of math is used for numbers with decimal points, which are important for things like 3D graphics, audio, and scientific calculations. VFP helps these calculations happen quickly and accurately.

Advanced SIMD (Neon)

The Advanced SIMD extension, also known as Neon, is a powerful feature for multimedia and signal processing. SIMD stands for "Single Instruction, Multiple Data," meaning it can perform the same operation on many pieces of data at once. Neon can speed up tasks like MP3 audio decoding or video processing. It's included in many modern ARM chips, especially those in smartphones.

Security Features

TrustZone (for Cortex-A)

TrustZone Technology, found in newer ARM architectures, helps make devices more secure. It creates two "worlds" inside the processor: a "trusted world" and a "less trusted world." This prevents sensitive information from leaking from the trusted part of the system to the less trusted part.

Imagine your phone. The operating system you use every day runs in the "less trusted world." But important security features, like those for protecting your payments or digital content, run in the "trusted world." This helps keep your data safe.

TrustZone for Armv8-M (for Cortex-M)

This is a similar security feature for smaller ARM processors used in microcontrollers. It also creates secure and non-secure areas, but it's designed for devices that need to be very quick and responsive, like those in smart home gadgets.

No-Execute Page Protection

Since ARMv6, the architecture supports "no-execute page protection," or XN. This is a security feature that prevents certain parts of memory from running code. It helps protect against malicious software that tries to trick the computer into running harmful instructions from data areas.

Large Physical Address Extension (LPAE)

LPAE was added in 2011 to allow ARM processors to access more memory. It extended the physical address size from 32 bits to 40 bits, meaning the processor could "see" and use much more RAM. In 64-bit ARM processors, this address space can be even larger.

64/32-bit Architecture

Armv8-A: The Big Leap

Announced in 2011, Armv8-A was a huge change for ARM. It added a new 64-bit architecture called "AArch64" and a new set of commands called "A64." This means ARM processors can now handle much larger amounts of data and memory, making them even more powerful.

Armv8-A also allows older 32-bit apps to run on a 64-bit operating system. Apple was the first company to release a product with an Armv8-A compatible chip, the Apple A7 in the iPhone 5S. Armv8-A also made features like floating-point math and advanced SIMD (Neon) standard. It also added special commands for encryption, which helps keep your data private.

Armv9-A: Focus on Security

Announced in 2021, the Armv9-A architecture focuses even more on security. It aims to keep different parts of the system separate and secure, which is very important for modern devices.

Operating System Support

32-bit Operating Systems

Many operating systems have supported the 32-bit ARM architecture for a long time.

Older Operating Systems

The first ARM-based personal computer, the Acorn Archimedes, ran an operating system called RISC OS. Some early Acorn machines could also run a version of Unix.

Operating Systems for Embedded Devices

The 32-bit ARM architecture is used by many operating systems for small, specialized devices. These include:

- Android

- FreeRTOS

- Linux

- VxWorks

- Windows Embedded Compact

Operating Systems for Mobile Devices

The 32-bit ARM architecture was the main choice for most mobile operating systems, such as:

Some older mobile operating systems that are no longer actively developed also used 32-bit ARM, like iOS 10 and earlier, and Windows Phone.

Operating Systems for Desktops and Servers

The 32-bit ARM architecture is also supported by RISC OS and many Unix-like operating systems, including:

64-bit Operating Systems

With the rise of 64-bit ARM processors, many operating systems now support them.

Operating Systems for Embedded Devices

- INTEGRITY

- FreeRTOS

- QNX

Operating Systems for Mobile Devices

- Android supports 64-bit ARM (Armv8-A) from Android Lollipop (version 5.0) onwards.

- iOS supports 64-bit ARM from iOS 7 onwards. Since iOS 11, only 64-bit ARM processors and apps are supported.

Operating Systems for Desktops and Servers

- Linux kernel version 3.7 and later supports Armv8-A. Many Linux distributions now support 64-bit ARM, including Debian, Ubuntu, Fedora, and RHEL.

- FreeBSD, OpenBSD, and NetBSD also support 64-bit ARM.

- Windows 10 and 11 can run 32-bit and 64-bit ARM applications.

- macOS supports ARM starting with macOS Big Sur (late 2020), especially for Apple's own M-series chips.

Images for kids

-

An ARMv7 processor was used in older versions of the Raspberry Pi computer.

See also

In Spanish: Arquitectura ARM para niños

In Spanish: Arquitectura ARM para niños